Fig 8.6 dan Fig 8.7

- Memahami prinsip kerja Multiplexer

- Memahami rangkaian Multiplexer dan dapat disimulasikan pada Proteus

- Alat

- Ground

- Bahan

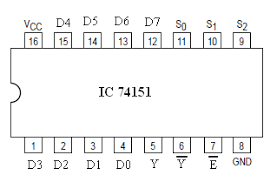

- IC 74151

IC 74151 merupakan IC multiplekser yang memiliki satu buah data selektor dengan delapan saluran masukan (D0 – D7) dan memiliki dua buah keluaran (Y – W).

Pada tabel kebenaran dapat dilihat bahwa:

1. Jika pin Enable diberi logika HIGH, maka apapun masukan dan apapun keadaan pin Select maka keluaran akan selalu berlogika LOW.

2. Jika pin Enable diberi logika LOW dan pin Select juga diberi logika LOW, maka akan ada salah satu masukan yang di salurkan ke keluaran.

3. Keluaran pada pin W adalah kebalikan dari keluaran pin Y.

- IC 74150

IC 74150 merupakan IC multiplekser yang memiliki satu buah data selektor dengan 16 saluran masukan (D0 – D15) dan memiliki satu saluran keluaran (W).

Pada tabel kebenaran dapat dilihat bahwa:

1. Jika pin Enable diberi logika HIGH, maka apapun masukan dan apapun keadaan pin Select maka keluaran akan selalu berlogika LOW.

2. Jika pin Enable diberi logika LOW dan pin Select juga diberi logika LOW, maka akan ada salah satu masukan yang di salurkan ke keluaran.

3. Logika keluaran pada pin W adalah kebalikan dari logika masukan.

- Gerbang NOT hanya memerlukan sebuah Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang NOT disebut juga dengan Inverter (Pembalik) karena menghasilkan Keluaran (Output) yang berlawanan (kebalikan) dengan Masukan atau Inputnya. Berarti jika kita ingin mendapatkan Keluaran (Output) dengan nilai Logika 0 maka Input atau Masukannya harus bernilai Logika 1. Gerbang NOT biasanya dilambangkan dengan simbol minus (“-“) di atas Variabel Inputnya.

- Gerbang logika AND ( IC 4081 )Gerbang AND (IC 4081) memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang AND akan menghasilkan Keluaran (Output) Logika 1 jika semua masukan (Input) bernilai Logika 1 dan akan menghasilkan Keluaran (Output) Logika 0 jika salah satu dari masukan (Input) bernilai Logika 0.Konfigurasi pin :

- Pin 7 adalah suplai negatif

- Pin 14 adalah suplai positif

- Pin 1 & 2, 5 & 6, 8 & 9, 12 & 13 adalah input gerbang

- Pin 3, 4, 10, 11 adalah keluaran gerbang

Spesifikasi :- Catu daya : 3 V - 15 V

- Fungsi : Quad 2-Input AND Gate

- Propagation delay : 55 ns

- Level tegangan I/O : CMOS

- Kemasan : DIP 14-pin Gerbang Logika OR ( IC 4071)

OR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila salah satu, sebagian atau semua inputnya berlogika 1.Konfogurasi Pin :- Resistor

- Logic Probe

- Logic State

- S = 0, ekspresi Boolean untuk output menjadi Y = I0.

- S = 1, ekspresi Boolean untuk output menjadi Y = I1.

.png)

Contoh Penggunaan 2-to-1 Multiplexer dengan ENABLE:

Multiplexer 2-to-1 dengan sinyal ENABLE digunakan untuk memilih salah satu dari dua input data (I₀ atau I₁) berdasarkan nilai sinyal seleksi (S), namun hanya jika ENABLE (EN) bernilai 1. Jika EN = 0, maka output Y = 0 (tidak aktif).

Misalnya diberikan kondisi berikut:

-

I₀ = 1

-

I₁ = 0

-

S = 0

-

EN = 1

Maka berdasarkan prinsip kerja rangkaian:

-

Karena EN = 1, maka output aktif.

-

Karena S = 0, maka input yang dipilih adalah I₀.

-

Maka Y = I₀ = 1

1) Sebuah rangkaian 2-to-1 multiplexer digunakan untuk memilih salah satu dari dua input, I₀ atau I₁, berdasarkan sinyal seleksi (S). Namun, multiplexer hanya akan aktif jika input ENABLE (EN) bernilai 1. Jika EN = 1, S = 0, I₀ = 1, dan I₁ = 0, berapakah nilai output Y?

Jawab:

Langkah-langkah penyelesaian:

Langkah 1 – Analisis kondisi ENABLE

-

EN = 1 → Multiplexer aktif, output akan mengikuti salah satu input berdasarkan nilai S.

Langkah 2 – Tentukan input yang dipilih

-

S = 0 → Maka input yang dipilih adalah I₀.

Langkah 3 – Tentukan output berdasarkan I₀

-

I₀ = 1 → Maka output Y = 1

Jadi output akhirnya:

-

Y = 1

6. Soal Pilihan Ganda[Kembali]

Pada rangkaian 2-to-1 multiplexer dengan ENABLE seperti gambar Fig. 8.6, apa yang terjadi jika EN = 0?

A. Output mengikuti nilai I₀

B. Output mengikuti nilai I₁

C. Output selalu bernilai 1

D. Output selalu bernilai 0 ✅

E. Tidak dapat ditentukan

1. Fig 8.6 2-to-1 Multiplexer with an ENABLE Input

Saat EN = 0, output Y akan selalu bernilai 0, terlepas dari nilai S, I₀, atau I₁. Hal ini disebabkan oleh adanya gerbang AND yang mengendalikan jalur sinyal berdasarkan ENABLE. Ketika ENABLE tidak aktif, sinyal dari input tidak akan diteruskan ke output.

Ketika EN = 1, maka MUX akan beroperasi sesuai fungsinya:

-

Jika S = 0, maka input I₀ akan dipilih dan diteruskan ke output.

-

Jika S = 1, maka input I₁ yang akan diteruskan ke output.

Secara logika, rangkaian ini terdiri dari:

-

Satu NOT gate untuk membalikkan sinyal S → menjadi S̅.

-

Dua AND gate untuk mengontrol alur sinyal I₀ dan I₁:

-

I₀ AND S̅ AND EN

-

I₁ AND S AND EN

-

-

Satu OR gate untuk menggabungkan dua jalur dan menghasilkan output akhir Y.

Dengan demikian, rumus logika untuk output Y adalah:

.png)

.png)

.png)

.png)

Komentar

Posting Komentar